## <u>INTRODUCTION TO COMPUTER TECHNOLOGIES</u> <u>Arithmetic Circuits PRETEST</u>

| 1) | The most significant bit of the binary number 100000 is                             |

|----|-------------------------------------------------------------------------------------|

| 2) | What is the sum of the binary numbers 1111 and 0011?                                |

| 3) | What is the difference between the binary numbers 1110110 and 1010?                 |

| 4) | The binary numbers 1110110 equals in decimal?                                       |

| 5) | A half-adder contains a(n) and a(n) gate.                                           |

| 6) | A full-adder contains two circuits.                                                 |

| 7) | A full-adder has inputs and outputs.                                                |

| 8) | A 4-bit parallel adder requires                                                     |

| 9) | additional gate(s) are required to convert a half-adder into a half-<br>subtractor. |

10) Full-adder and Full-subtractor are classified as \_\_\_\_\_\_ circuits.

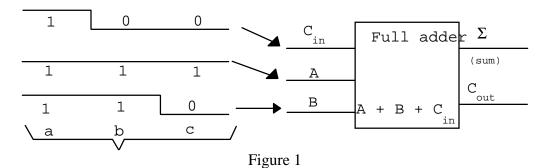

## Refer to Fig. 1 (below) for questions 11 - 16.

- 12) The  $C_0$  output from the full-adder circuit for problem <u>a</u> will be \_\_\_\_\_ (1 bit).

- 13) The sum output from the full-adder circuit for problem  $\underline{b}$  will be \_\_\_\_\_ (1 bit).

- 14) The  $C_0$  output from the full-adder circuit for problem <u>b</u> will be \_\_\_\_\_ (1 bit).

- 15) The sum output from the full-adder circuit for problem  $\underline{c}$  will be \_\_\_\_\_ (1 bit).

- 16) The  $C_0$  output from the full-adder circuit for problem <u>c</u> will be \_\_\_\_\_ (1 bit).

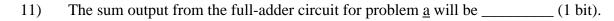

## Refer to Fig. 2 (below) for questions 17 - 25.

## Figure 2

| 17) | When this unit is adding 1001 to 0101, the control must be                                                                                                                     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18) | When this unit is adding 1001 to 0101, the output sum appears as binary (4 bits).                                                                                              |

| 19) | When this unit is adding 1001 to 0101, the $C_{in}$ input to the full-adder is owing to the disabled AND gate                                                                  |

| 20) | The XOR gates function as gates when the control is high (unit in subtract mode).                                                                                              |

| 21) | When this unit is in subtract mode, the end-around carry technique is used to allow the adders to perform binary subtraction.                                                  |

| 22) | When this unit is subtracting 1010 from 1100, the bits appearing at the B inputs to the full adders will be [4 bits, with the 8s bit on the left and the 1s bit on the right]. |

| 23) | When this unit is subtracting 1010 from 1100, the difference appearing at the output will be binary [4 bits].                                                                  |

| 24) | When this unit is subtracting 1010 from 1100, the end-around carry line will be (HIGH, LOW).                                                                                   |

- 25) This unit can be best described as a(n) \_\_\_\_\_\_ adder/subtractor.

- 26) What is the binary product of 1010 X 0111?

- 27) What is the binary product of 1111 X 0101?

- 28) What is the product of  $1101_2 \times 2_{10}$  (in binary)?

- 29) What is the product of  $1010_2 \times 3_{10}$  (in binary)?

- 30) The 1s complement number 0101 represents \_\_\_\_\_\_ in decimal.

- 31) The 1s complement number 1011 represents \_\_\_\_\_\_ in decimal.

- 32) The decimal 13 equals \_\_\_\_\_ (4 bits) in 1s complement.

- 33) The decimal 3 equals \_\_\_\_\_ (4 bits) in 1s complement.

- 34) When microprocessors process both positive and negative numbers, \_\_\_\_\_\_ representation are used.

- 35) The 2s complement number 0101 represents a positive \_\_\_\_\_ in decimal.

- 36) The 2s complement number 1111 represents a negative \_\_\_\_\_\_ in decimal.

- 37) In 2s complement, the MSB is called the \_\_\_\_\_ bit.

- 38) The decimal -3 equals \_\_\_\_\_ (4 bits) in 2s complement.

- 39) The decimal 6 equals \_\_\_\_\_ (4 bits) in 2s complement.

- 40) The decimal -2 equals \_\_\_\_\_ (4 bits) in 2s complement.

- 41) The sum of the 2s complement numbers 1011 & 1110 equals \_\_\_\_\_ (4 bits) in 2s complement.

- 42) Subtract 2s complement numbers 0011 from 2s complement numbers 1011 (Give answer in 2s complement).

- 43) Subtract 2s complement numbers 0011 from 2s complement numbers 0111 (Give answer in 2s complement).

- 44) A five bit adder requires \_\_\_\_\_ half adder(s) and \_\_\_\_\_ full adder(s).

- 45) A seven bit subtractor requires \_\_\_\_\_ half subtractor(s) and \_\_\_\_\_ full subtractor(s).

- 46) A five bit parallel adder/subtractor requires \_\_\_\_\_ half adder(s), \_\_\_\_\_ full adder(s), \_\_\_\_\_ full adder(s), \_\_\_\_\_ half subtractor(s) and \_\_\_\_\_ full subtractor(s).